### Exercise of Electronics for Communication Systems Prof. C. Abbate, G. Busatto - A.A. 2018/2019 **10 – Experimental characterization of the integrated PLL (HCF4046B)** 29/11/2018 – Diego Tuzi – 50435 – diego.tuzi@studentmail.unicas.it

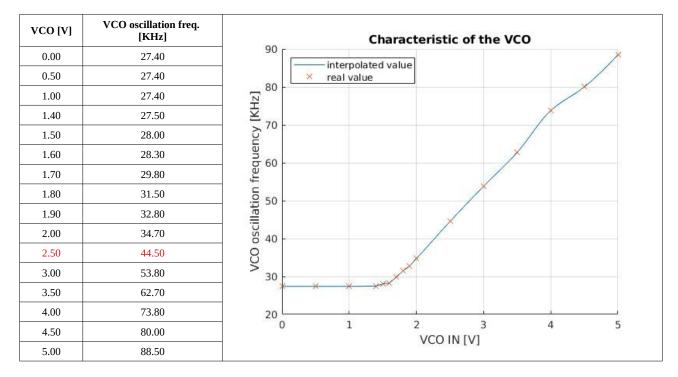

#### **TEST OF VCO OPERATION**

Place the components R1, R2 and C1 on the board. The supply voltage is 5 V. Connect the voltage supplied by the second section of the power supply to the pin 9 (VCO IN). In alternative use a second power supply. Measure the characteristic of the VCO. For this purpose measure the oscillation frequency of the VCO for VCO IN variable between 0 and 5V with 0.5V steps.

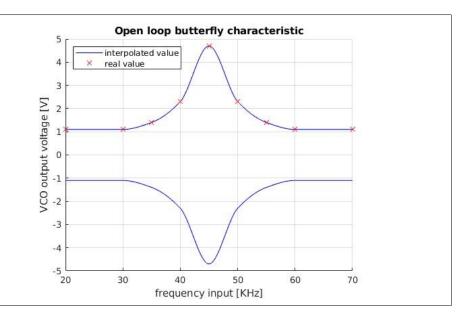

## **OPEN LOOP BUTTERFLY CHARACTERISTIC**

Remove R3 e C2 and connect the supplied external RC circuit in order to leave open the feed-back loop. Supply pin 9 (VCO IN) with a voltage of 2.5 V given by the second section of the power supply. Supply pin 14 (BNC connector IN) with a square waveform given by a signal generator with the amplitude of 4.5 V and duty-cycle 50%. Measure the characteristic Vc= g(fi) (the voltage across C2), where fi is the frequency of the input signal. Do it for phase comparators I. For measuring the characteristic connect the oscilloscope probes to "BNC connector IN" and capacitor C2.

| Vc= g(fi) [V] |

|---------------|

| 1.10          |

| 1.10          |

| 1.40          |

| 2.30          |

| 4.70          |

| 2.30          |

| 1.40          |

|               |

## Exercise of Electronics for Communication Systems Prof. C. Abbate, G. Busatto - A.A. 2018/2019 **10 – Experimental characterization of the integrated PLL (HCF4046B)** 29/11/2018 – Diego Tuzi – 50435 – <u>diego.tuzi@studentmail.unicas.it</u>

Do it for phase comparators II. For measuring the characteristic connect the oscilloscope probes to "BNC connector IN" and capacitor C2.

Using phase comparator II, circuit is unstable.

# **CLOSED LOOP BUTTERFLY CHARACTERISTIC**

Close the feedback loop disconnecting the external RC and then connecting the components R3, C2 in the specific sockets.

Select phase comparator II (Jumper SELECT COMP on COMP2).

Supply pin 14 (BNC connector IN) with a square waveform given by a signal generator with amplitude 4.5 V and duty-cycle 50%.

Starting from low input frequencies fi (100Hz) visualize the voltage waveform on pin 10 (DEM OUT) which reproduce the voltage at pin 9 (VCO IN) thanks to a voltage follower present in the integrated circuit. Measure the amplitude of VCO IN varying fi in order to identify the capture and holding frequency for increasing fi.

As you can expect from Design Information Datasheet frequency lock range and frequency hold in range are the same using Phase Comparator II.

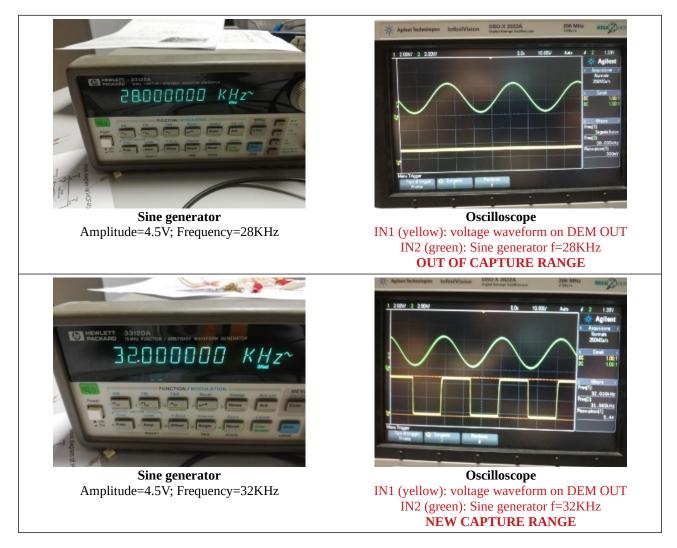

| f <sub>L</sub> min | f <sub>L</sub> max | f <sub>H</sub> min | f <sub>H</sub> max |

|--------------------|--------------------|--------------------|--------------------|

| 28 KHz             | 89 KHz             | 28 KHz             | 89 KHz             |

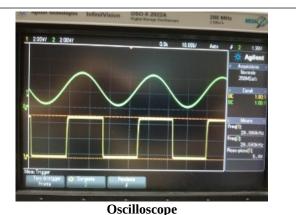

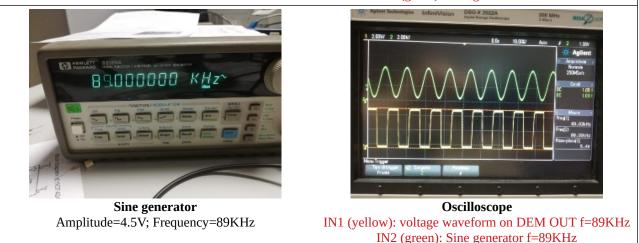

Sine generator Amplitude=4.5V; Frequency=28KHz

IN1 (yellow): voltage waveform on DEM OUT f=28KHz IN2 (green): Sine generator f=28KHz

# Exercise of Electronics for Communication Systems Prof. C. Abbate, G. Busatto - A.A. 2018/2019 **10 – Experimental characterization of the integrated PLL (HCF4046B)** 29/11/2018 – Diego Tuzi – 50435 – <u>diego.tuzi@studentmail.unicas.it</u>

Identify capture and hold ranges of the PLL having selected the phase discriminator I (Jumper SELECT COMP on COMP1).

| As you can expect from Design Information Datasheet frequency lock range and frequency hold in range are different using Phase Comparator I. In particular lock range is contained in hold-in range. |           |                    |                    |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|--------------------|--|--|

| f <sub>L</sub> min                                                                                                                                                                                   | $f_L max$ | f <sub>H</sub> min | f <sub>H</sub> max |  |  |

| 32 KHz                                                                                                                                                                                               | 58 KHz    | 28 KHz             | 86 KHz             |  |  |

Verify the existence of secondary capture ranges for higher values of fi.

| PLL locks is able to lock in other frequency range, but the followed frequencies are wrong. |           |                    |                    |  |  |

|---------------------------------------------------------------------------------------------|-----------|--------------------|--------------------|--|--|

| f <sub>L</sub> min                                                                          | $f_L max$ | f <sub>H</sub> min | f <sub>H</sub> max |  |  |

| 121 KHz                                                                                     | 147 KHz   | 92 KHz             | 180 KHz            |  |  |

## Exercise of Electronics for Communication Systems Prof. C. Abbate, G. Busatto - A.A. 2018/2019 **10 – Experimental characterization of the integrated PLL (HCF4046B)** 29/11/2018 – Diego Tuzi – 50435 – <u>diego.tuzi@studentmail.unicas.it</u>

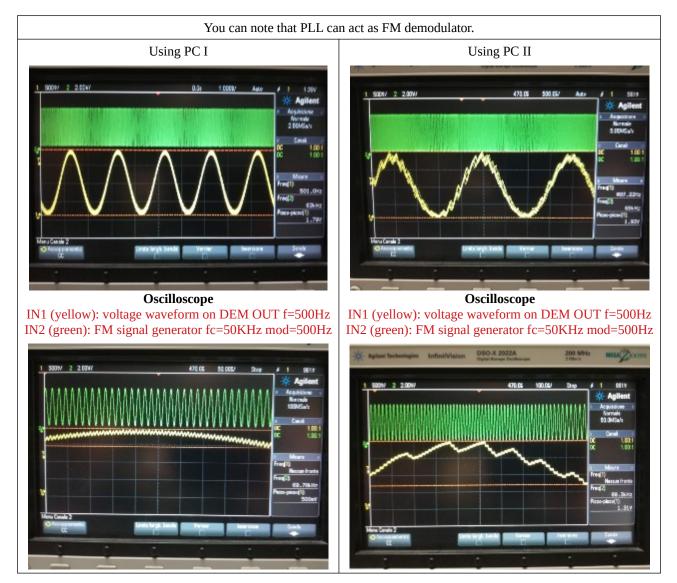

# FREQUENCY DEMODULATOR

Feed the input of the PLL with an FM signal with the carrier at 50kHz modulated with a sinusoidal signal at 500Hz, obtained by the HP function generator. Visualize the waveforms on the oscilloscope at the pin DEM OUT.